电子芯片的良率详解

一、半导体制程“良率”的定义

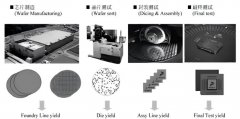

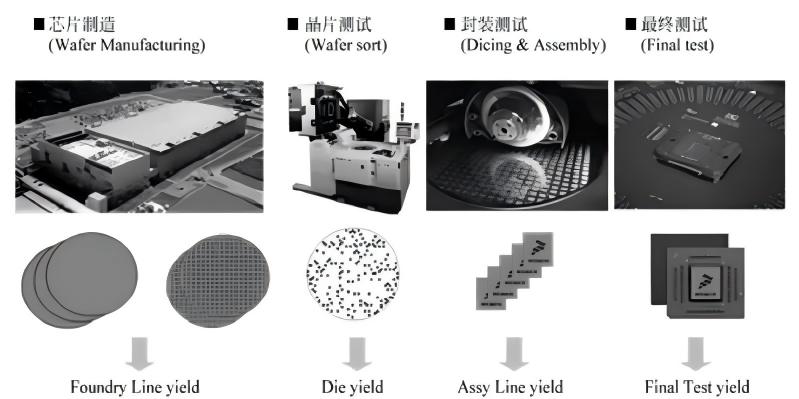

良率(yield)也称为“合格率”,是一个量化失效的产品质量指标,指合格品量占全部加工品的百分率。通常也是工艺改善最重要的指标。在半导体工艺中,生产线良率表征的是晶圆从下线到成功出厂的概率;晶圆良率表征的是一片晶圆上的芯片合格率。生产线良率乘以晶圆良率就是总良率。而在半导体生产制造的各个环节中,都可能会引起最终产品的失效。下图所示为半导体生产环节中的各种yield。

半导体生产环节中的各种yield

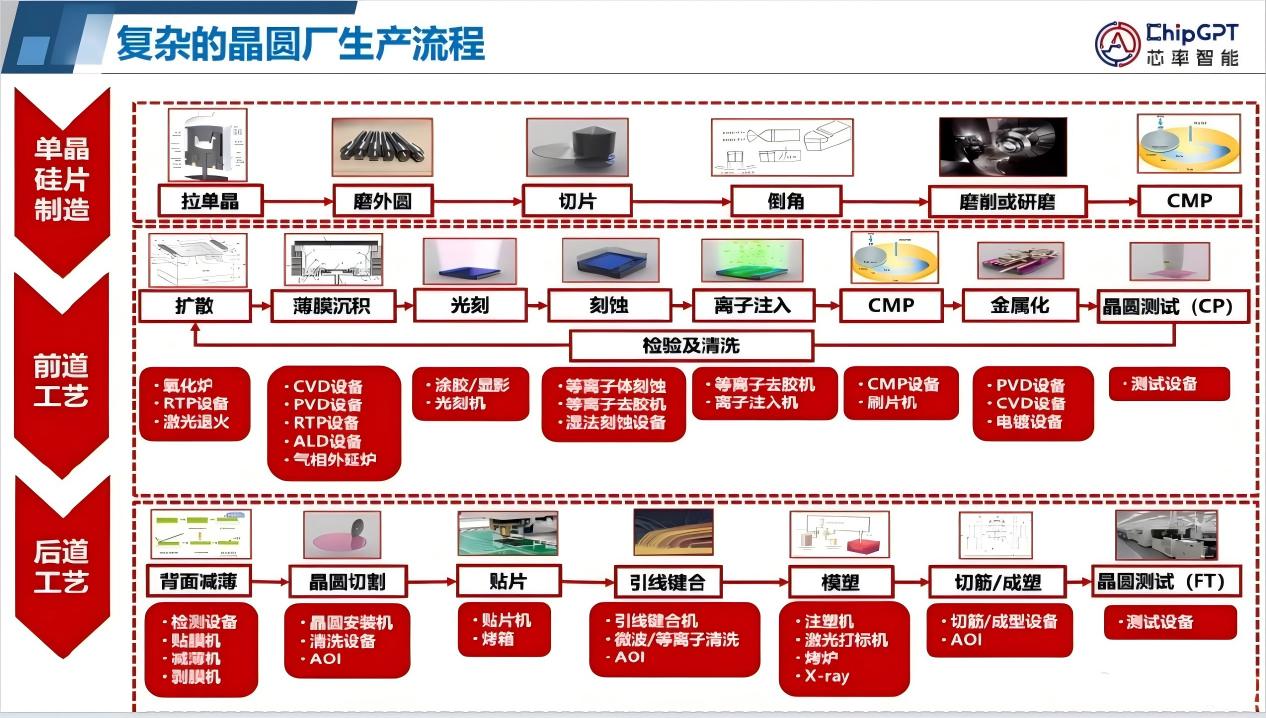

在半导体生产制造中,yield的定义为:

yield可以基于晶粒(die)或者晶片(wafer)或者批次(lot)定义。定义在wafer或者lot上的yield,一般反映生产工艺中的控制问题,如操作人员的误操作,设备故障等,通常也称为生产线良率(line yield)。例如,生产线下线1000片wafer,最后由于各种原因报废(scrap)20片wafer,那么line yield就等于98%。

机制分类对于工艺引起的yield loss,按照失效的特征分为两大类:参数性 (parametric)和功能性(functional)失效。一般的理解,功能性失效,往往由于物理缺陷引起,习惯上也被称为hard fail或者缺陷性失效;参数性失效,往往由于器件电参数的不优化或者漂移超出规格引起,习惯上也被称为soft fail。对于功能性失效,根据在wafer表面的空间分布特征(spatial distribution),又可分为随机性(random)和系统性(systematic)失效。

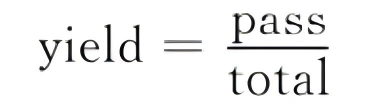

二、关乎晶圆厂生死的晶圆(Wafer)检验良率

对于半导体工厂来说,良率这个概念比其他业种还来得具有特别的含意。为什么呢?如下图所示,半导体生产的良率通常可分别为各个种类,其随着构成半导体的制程,也就是在矽晶圆上把多数的半导体制作上去的“前段制程”,以及针对晶圆上的半导体晶片进行良品与否判定的“晶圆检验制程”,加上将晶圆分割成一个一个晶片,并收纳到包装后进行检查的“组装、检验制程”,性质及方法均有大幅差异。

前段制程(扩散制程)的良率,也就是投入生产线的矽晶圆中,完成前段制程的晶圆的比例,即称为“前段制程良率”。另外,在投入组装制程的IC晶片总数中,能够通过最终检验并入库的合格晶片的比例,称为“后段制程良率”。当然上述这些良率也很重要,但更重要的是,“从每一片完成前段制程的晶圆中,可以取得多少良品晶片”,这也称为“晶圆检验良率”,具有特的意义。

此处的良率(Y),可以一片晶圆上拥有的有效晶片数(N)及良品机率(P),表示为以下公式:Y=N*P。此处的有效晶片N的计算,多用于高精细的设计标准且大口径的晶圆。

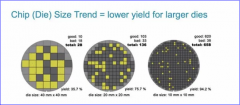

另外,良品机率P,则因微尘、损伤、脏污、及制程导致的缺陷密度(每单位晶圆面积上具有的致命缺陷数)决定之。其结果如下图所示,良率Y(=G/W)不但直接反应了半导体的制造成本,也成为设计、制造上的制程、材料、装置、管理等综合指标。

因此,良率的管理一直都是晶圆厂的关键环节,芯片巨头都将先进制程作为竞争的目标,一方面是将摩尔定律奉为圭臬,力争做到功耗、性能和面积的平衡,另一方面先进制程逐渐演变为厂商的营销策略。但更先进的制程长期以来代表着技术的领先性,以及更高的性能和更低的功耗。芯片制程从微米时代进入纳米时代,目前制程线宽已经降到5nm,甚至是3nm以下。

随着特征尺寸的不断微缩,逐渐达到了半导体制造设备和制程工艺的极限,目前,集成电路的晶体管数量,以及功耗和性能已经很难像过去40年那样,顺畅地按照摩尔定律演进,很大程度上源于工艺难度越来越大,成本也高得吓人。为了解决高昂的成本问题,厂商开始严格控制半导体制造过程中的产品良率。直接来说,良率直接影响到最终的实际成本,良率越高,最终实际分摊到每一颗正常芯片上的成本就越低。对于尖端的逻辑晶圆厂来说1%良率的提升意味着将近1.5亿美金左右的利润提升。

如果将先进制程的研发视为芯片巨头们之间的竞争,那么提高芯片良率则可以视为芯片厂商的自我竞赛,一方面是因为良率作为芯片厂商的最高机密数据十分敏感,不会像公布工艺节点那样公布自家真实良率情况,另一方面是影响良率的因素众多,很难有一个准确的数值与竞争对手进行比较,而芯片厂商始终致力于能够在短时间内就向客户交付安全正常的芯片,提升良率需要争分夺秒。

三、良率管理是摩尔定律的另一种延续

之所以说提升芯片良率与制程开发同等重要,除了提升良率是芯片从实验室阶段到量产的必经之路以及芯片良率与整体成本密切相关之外,从经济角度上讲,提升芯片良率可以视为摩尔定律的另一种延续。

需要注意的是,芯片制造的良率跟产品的合格率是有一定区别的,芯片制造过程中会引入各种各样的不确定因素,流程缺陷、环境中的颗粒物、工艺的波动,最终生产出来的产品会有一些不确定性,最终的产品不满足这些指标就没办法正常交付,正常产品的占比就是良率。

产品合格率,更偏一个质量概念,即卖出去的良品失效的比例,这是对封装工厂的重要考核指标,主要取决于工厂的技术和管理水平。另外,先进设备端的良率管理跟产线的良率管理也存在一定的区别,虽然两者有一定的交叉重叠,但设备端的良率分析处理更多的是影响某个环节的良率处理能力,对于整条产线的良率提升还是需要上一层的制程良率管理软件。

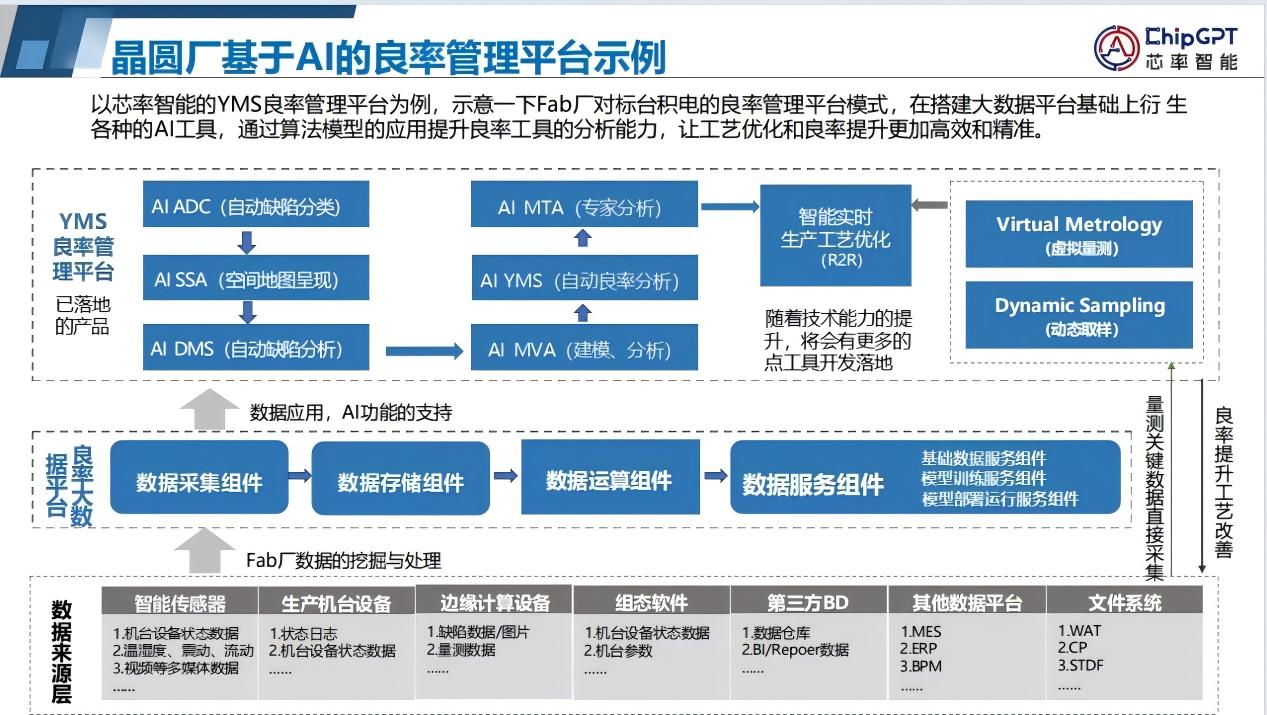

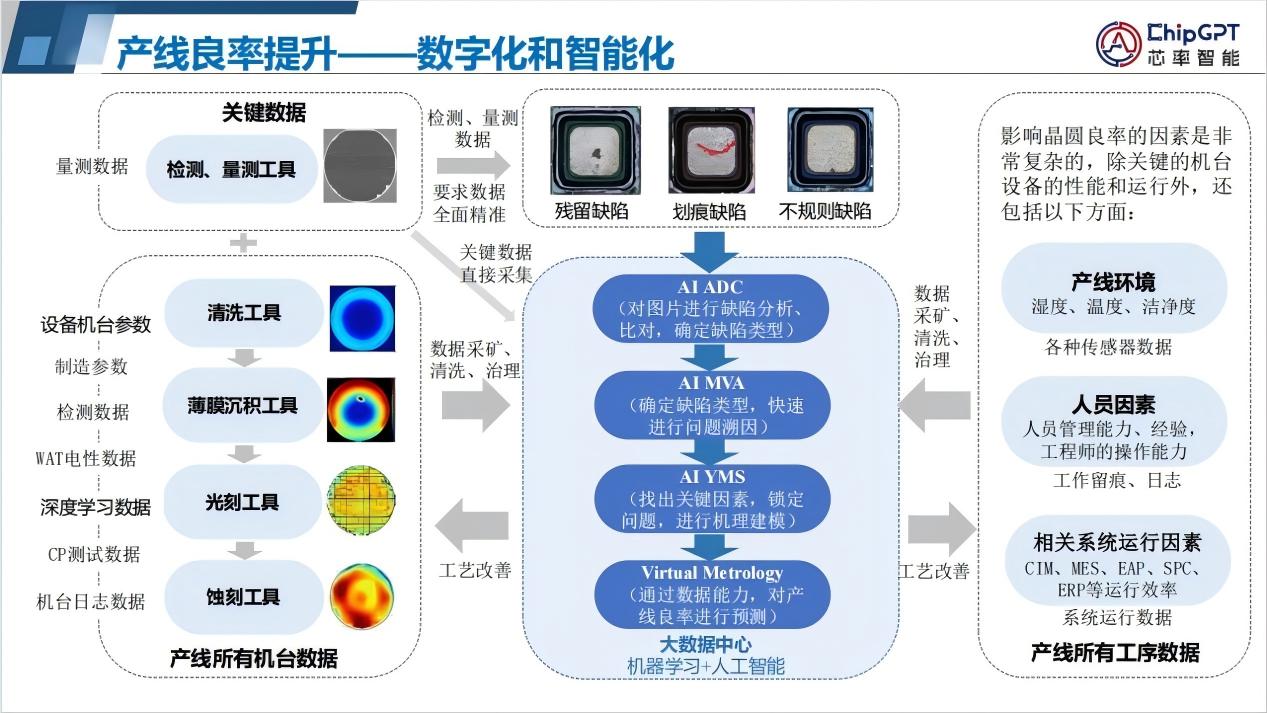

应用比较广泛的半导体制造良率管理系列软件包括:良率(缺陷)管理系统 YMShttps://www.semiw.com/dMS、自动缺陷分类 ADC、动态取样 DynamicSampling、多参数溯因分析 MVA、晶圆工艺控制-量测 Metrology等。

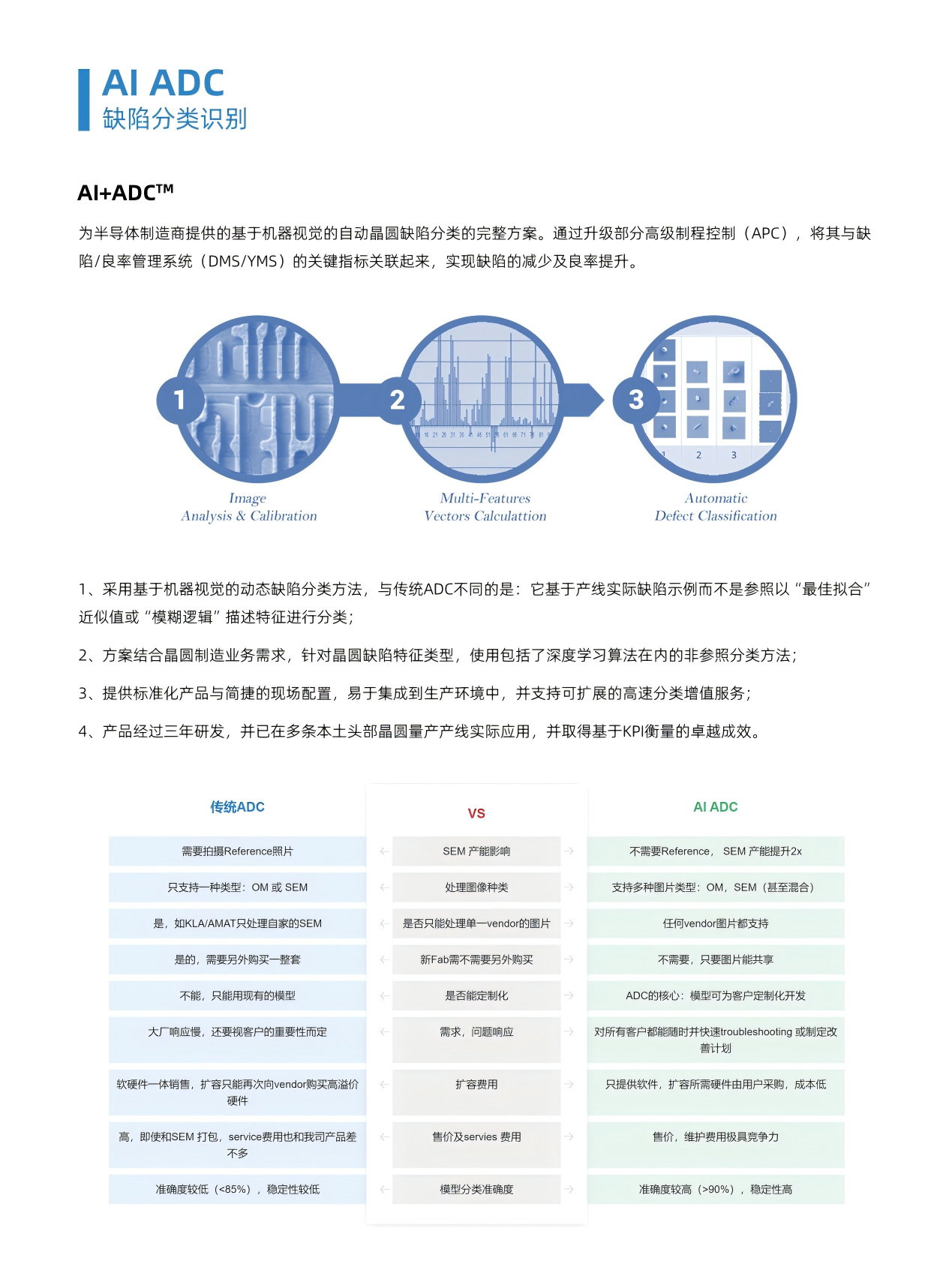

芯率智能服务国内头部晶圆厂达20年,在致力于实现晶圆制造的工艺优化和良率提升的同时,发挥自身优势,推动芯片设计和制造协同。目前我们的AI ADC产品已经在国内头部的晶圆厂中进行了部署,并得到了实地验证,取得了良好的效果。AI ADC产品是为半导体制造商提供的基于机器视觉的自动晶圆缺陷分类的完整方案。通过升级部分高级制程控制(APC),将其与缺陷/良率管理系统(DMS/YMS)的关键指标关联起来,实现缺陷的减少及良率提升。

芯片头条

-

三星2纳米工艺落后台积电,良率低致客户流向台积电

2026-04-16 -

英伟达多元产品线分攻AI训练与推理需求,以应对CSP自研ASIC规模升级

2026-03-27 -

AI动能稳健,预估2026年晶圆代工产值年增24.8%,部分制程涨价浮现

2026-03-27 -

中国信息通信研究院:具身智能领域首个行业标准正式发布

2026-03-27 -

存储芯片供不应求,苹果公司采购价格翻倍

2026-02-21